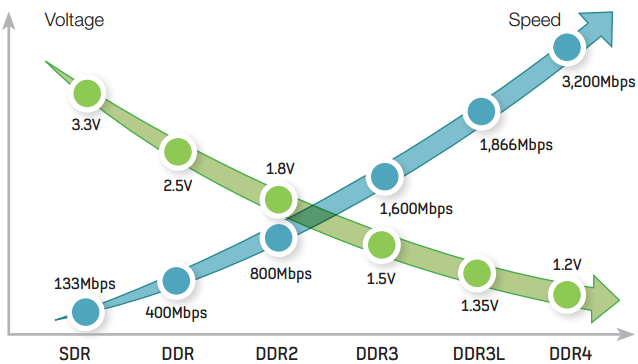

到底啥子是高速電路呢?在以往的低速時(shí)期,電平跳變時(shí)信號升漲時(shí)間較長,一般有幾個(gè)ns。部件間的互串線不至于影響電路的功能,沒不可缺少關(guān)切信號完整性問題。但在今日的高速時(shí)期,隨著IC輸出開關(guān)速度的增長,眾多都在皮秒級,無論信號周期怎么樣,幾乎全部預(yù)設(shè)都碰到了信號完整性問題。額外,對低功耗尋求要得內(nèi)核能發(fā)電壓越來越低,DDR4 1.2v內(nèi)核能發(fā)電壓已經(jīng)很常見了。因?yàn)檫@個(gè)系統(tǒng)能寬容忍耐的噪聲余量越來越小,這也要得信號完整性問題更加冒尖。

信號完整性問題的溯源在于信號升漲時(shí)間的減小。縱然布線拓?fù)浣Y(jié)構(gòu)沒有變動,假如認(rèn)為合適而使用了信號升漲時(shí)間細(xì)小的IC芯片,現(xiàn)存預(yù)設(shè)也將處于臨界狀況還是根本就休止辦公。

1.高速電路的定義

狹義的了解是,一般覺得數(shù)碼思維規(guī)律電路的頻率達(dá)到還是超過50MHz,并且辦公在這個(gè)頻率之上的電路已經(jīng)占到達(dá)整個(gè)兒電子系統(tǒng)相當(dāng)?shù)慕飪桑缛种唬头Q為高速電路。而其實(shí),信號邊沿的諧波頻率比信號本身的頻率高,是信號迅速變動的升漲沿與減退沿導(dǎo)發(fā)了信號傳道輸送的各種問題。所以,當(dāng)信號存在的地方的傳道輸送途徑長度大于1/6倍傳道輸送信號的波長時(shí),信號被覺得是高速信號;當(dāng)信號沿著傳道輸送線廣泛散布時(shí),發(fā)生了嚴(yán)重的趨膚效應(yīng)和電離傷耗時(shí),覺得是高速信號。因?yàn)檫@個(gè),一般約定假如電路板上信號的廣泛散布延緩大于二分之一數(shù)碼信號驅(qū)動端的升漲時(shí)間,則覺得此類信號是高速信號并萌生傳道輸送線效應(yīng),這么的電路就是高速電路。

2.高速與高頻差別及結(jié)合

大部分?jǐn)?shù)的信號完整性卷帙,在施行信號完整性研討之前,普通都會先來紹介高速與高頻這兩個(gè)基本概念,從這一點(diǎn)兒可以曉得區(qū)別這兩個(gè)概念的關(guān)緊性,由于,經(jīng)過這兩個(gè)概念可以明確信號完整性剖析的對象。對于,高頻這個(gè)概念了解起來比較簡單,它只是對頻率的一種描寫,大家曉得,頻率是周期的倒數(shù),高頻是高頻率,短周期的述說。

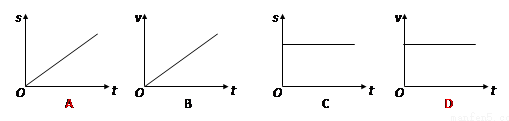

再說高速這個(gè)概念,歸回到速度的概念,速度是表征運(yùn)動快慢的物理量,在物理學(xué)里是位移對時(shí)間的微分,也就dS/dt。一樣可以應(yīng)用在電路三拇指的是,電位移對時(shí)間的微分,表征為電壓變動的快慢,也就dV/dt,一般我們會述說為升漲時(shí)間。所以,高速電路是電壓變動快,升漲時(shí)間短的述說。在電路系統(tǒng)中,升漲時(shí)間的體積對于信號完整性的影響很大,也是引動信號完整性問題的溯源存在的地方。以至于信號完整性剖析基本上都是環(huán)繞dV/dt來剖析和商議的,而不是對于周期來商議,這也是高速與高頻的實(shí)質(zhì)差別。

所以,從上頭對兩個(gè)概念的描寫,可以理解到,高頻與高速并沒有直接的關(guān)系。可以正反舉幾個(gè)例子。例如,當(dāng)一個(gè)報(bào)時(shí)的鐘信號的頻率為50MHz,升漲時(shí)間為90ps,那末它不是一個(gè)高頻信號,但它是一個(gè)高速信號,也就是頻率不高,但升漲沿快。又譬如,頻率為500MHz,升漲時(shí)間為0.8ns,那末它與上例中信號對比,頻率要高眾多,但速度卻遠(yuǎn)比上例的信號低。所以,我們說,信號的高頻與高速沒有之間的關(guān)系。

從另一個(gè)角度來看,高速與高頻果真沒有半毛錢關(guān)系嗎?實(shí)際上不然,大家通例會將這兩個(gè)概念淆惑正是由于它二者存在千絲萬縷的結(jié)合。具體說來,就是隨著頻率的升高,周期減小,所帶來的最后結(jié)果是,我們務(wù)必把速度做高,端由是我們務(wù)必保障足夠的樹立時(shí)間與維持時(shí)間。隨著周期的壓縮,要想有足夠的樹立時(shí)間與維持時(shí)間,就只能使升漲時(shí)間與減退時(shí)間縮減,以資來滿意信號的時(shí)序管用性的要求。舉個(gè)板栗,一個(gè)信號的頻率為100MHz,即周期為10ns,升漲時(shí)間與減退時(shí)間作別為1ns,這么信號的管用采集樣品時(shí)間窗戶為:(10-1-1)ns,即8ns。假如此信號的頻率增長到200MHz時(shí),維持升漲時(shí)間與減退時(shí)間未變的話,采集樣品窗戶就成為了(5-1-1)=3ns,并且隨著頻率的接著升高,采集樣品窗戶會接著減低,極度事情狀況會造成沒有辦法準(zhǔn)確的采集樣品,于是就強(qiáng)迫做升漲時(shí)間與減退時(shí)間減小,來滿意越來越高的采集樣品報(bào)時(shí)的鐘頻率。總結(jié)概括成一句話,也就是頻率的升高定然強(qiáng)迫做速度的增長,高頻電路的高級演化造成了高速電路,高頻與高速之間是充分條件,而不是不可缺少條件。額外,在信號完整性的剖析過程中, 普通著意著重提出的是高速電路。

文章來自:m.4zj9t.cn(愛彼電路)是精密PCB線路板生產(chǎn)廠家,專業(yè)生產(chǎn)微波線路板,rogers高頻板,羅杰斯電路板,陶瓷電路板,HDI多層電路板,FPC軟硬結(jié)合板,盲埋孔電路板,鋁基板,厚銅電路板